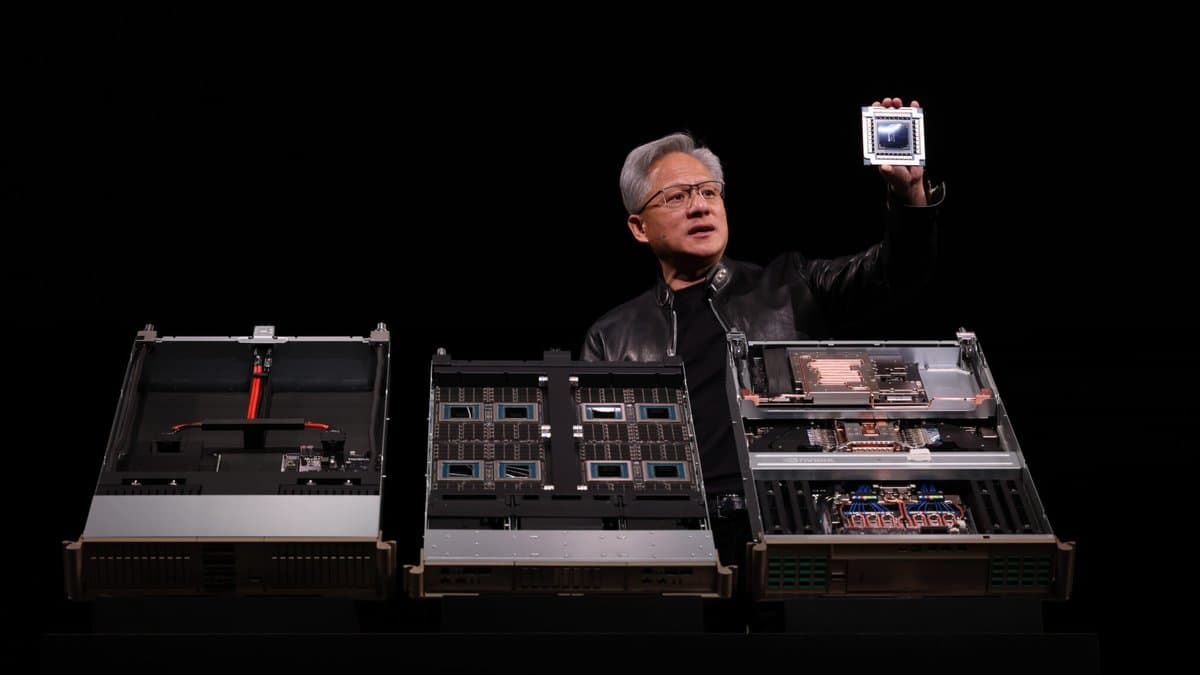

Nvidia GTC 2026: Vera Rubin 완전 해부 — 스펙, 가격, 로드맵 총정리

7개 신규 칩, 10배 전력 효율, $1T 주문 예고. Jensen Huang이 공개한 Vera Rubin 플랫폼의 모든 것을 스펙 테이블과 공식 소스로 정리했다.

"2027년까지 최소 $1T의 주문이 보인다"

Jensen Huang이 GTC 2026 키노트에서 한 말이다. 허풍이 아니라, Blackwell과 Vera Rubin을 합친 수주 전망이다. 3월 16일 산호세에서 열린 GTC 2026은 Nvidia 역사상 가장 큰 발표였다. 7개 신규 칩을 한 번에 공개하고, 자율주행에서 Disney까지 아우르는 파트너십을 쏟아냈다.

정리가 필요하다. 하나씩 뜯어보자.

배경: 여기까지 오기까지

Vera Rubin을 이해하려면 Nvidia 데이터센터 GPU의 진화 궤적을 알아야 한다:

| 세대 | 연도 | 핵심 혁신 |

|---|---|---|

| Volta (V100) | 2017 | 최초 텐서 코어(Tensor Core) |

| Ampere (A100) | 2020 | 3세대 텐서 코어, MIG(멀티 인스턴스 GPU) |

| Hopper (H100) | 2022 | 트랜스포머 엔진, FP8 |

| Blackwell (B200) | 2024 | 2다이 설계, FP4, NVLink 5 |

| Vera Rubin (R200) | 2026 | HBM4, NVLink 6, 50 PFLOPS |

각 세대가 와트당 추론 성능을 대략 2배씩 올려왔다. Vera Rubin은 2배가 아니라, Nvidia 주장으로 특정 AI 워크로드(대규모 MoE 모델 추론 등)에서 와트당 성능 10배 개선이다. 어떻게? 공정 미세화(3nm), 메모리 대역폭 도약(HBM4), 인터커넥트 강화(NVLink 6)라는 세 가지 핵심 아키텍처 전환이 동시에 이뤄졌기 때문이다.

Rubin GPU (R200) — 핵심 스펙

TSMC N3E(3nm Enhanced, 3nm 강화 공정) 노드에 3,360억 개 트랜지스터를 담았다. TSMC의 CoWoS-L(Chip on Wafer on Substrate with Local interconnect) 패키징 기술을 사용한다. 이 기술은 여러 다이(칩렛)를 하나의 실리콘 인터포저 위에 올려 초고속으로 연결하는 방식으로, 단일 거대 다이를 만드는 것보다 수율(yield)이 높고 설계 유연성도 뛰어나다.

| 항목 | Rubin (R200) | Blackwell (B200) | 개선 |

|---|---|---|---|

| 공정 | TSMC 3nm | TSMC 4nm | — |

| 트랜지스터 | 3,360억 개 | 2,080억 개 | 1.6x |

| 다이 구성 | 2 컴퓨트 + 2 I/O (CoWoS-L) | 2 컴퓨트 | — |

| HBM 메모리 | 288GB HBM4 (8스택) | 192GB HBM3e | 1.5x |

| 메모리 대역폭 | ~22TB/s | ~8TB/s | 2.8x |

| FP4 추론 성능 | 50 PetaFLOPS | ~10 PetaFLOPS | 5x |

| FP8 학습 성능 | ~25 PetaFLOPS | ~9 PetaFLOPS | ~2.8x |

| TDP | 2,300W (MaxP) | ~1,200W | — |

| 인터커넥트 | NVLink 6 | NVLink 5 | 대역폭 2.6x |

50 PetaFLOPS. GPU 한 장에서. Blackwell 대비 FP4 추론이 5배다.

HBM4란 무엇이고 왜 중요한가?

HBM(High Bandwidth Memory, 고대역폭 메모리)은 GPU 패키지 위에 직접 적층하는 DRAM으로, 실리콘 인터포저를 통해 연결된다. 세대마다 대역폭이 극적으로 증가해왔다:

- HBM2e (A100): 2TB/s

- HBM3 (H100): 3.35TB/s

- HBM3e (B200): ~8TB/s

- HBM4 (R200): ~22TB/s

HBM4는 근본적인 아키텍처 변화를 가져온다. 이전 세대까지는 메모리 컨트롤러가 GPU 다이에 내장되어 있어, GPU의 핀(pin) 수가 대역폭의 상한을 결정했다. HBM4에서는 최초로 컨트롤러 로직이 메모리 스택 자체(베이스 다이)로 이동했다. 이것이 의미하는 바:

- GPU 핀 수를 늘리지 않고도 더 높은 대역폭 달성

- 전력 효율 개선 -- 신호 경로가 짧아짐

- 더 유연한 메모리 구성 -- GPU 재설계 없이 다양한 HBM4 스택 크기 지원 가능

AI 추론에서 메모리 대역폭은 주된 병목(bottleneck)이다. 이를 "메모리 바운드(memory-bound)"라 하는데, 연산 능력은 남지만 메모리에서 데이터를 읽는 속도가 처리 속도를 제한하는 상황이다. 예를 들어 Llama-70B 같은 모델은 FP16 가중치만 약 140GB가 필요하고, 토큰 하나를 생성할 때마다 이 가중치를 메모리에서 읽어야 한다. 대역폭이 높을수록 초당 더 많은 토큰을 생성할 수 있다. 8TB/s에서 22TB/s로의 도약은 메모리 바운드 모델에서 약 2.75배 빠른 토큰 생성을 의미한다.

FP4란 무엇이고 왜 50 PFLOPS인가?

FP4(4비트 부동소수점)는 프로덕션 AI 추론에서 사용되는 가장 낮은 정밀도 형식이다. 숫자 하나에 FP16의 16비트나 FP32의 32비트 대신 단 4비트만 사용한다. 트레이드오프는 명확하다: 정밀도가 낮아지면 정확도가 다소 떨어지지만, FP16 대비 클럭당 4배 더 많은 연산이 가능하다.

현대적 양자화 기법(GPTQ, AWQ, GGUF Q4_K_M)은 잘 보정된 4비트 모델이 대부분의 작업에서 전체 정밀도 대비 95~99%의 품질을 유지한다는 것을 보여줬다. 따라서 50 PFLOPS의 FP4는 이론적 수치가 아니라, 실제 추론 워크로드에 직접 적용 가능한 성능이다.

Vera CPU — Nvidia 자체 설계 ARM

GPU만 바뀐 게 아니다. CPU도 새로 만들었다. 대부분의 보도가 놓치고 있지만, 이건 상당히 큰 변화다. Nvidia는 2023년부터 ARM 기반 Grace CPU를 사용했지만, Vera는 Nvidia가 코어를 처음부터 직접 설계한 최초의 CPU다.

- 88코어 NVIDIA Olympus (커스텀 ARM Neoverse 파생 설계)

- Spatial Multithreading: 코어당 2개 스레드 동시 실행 (Intel의 하이퍼스레딩과 유사하지만 아키텍처적 차이 있음)

- 메모리 대역폭: LPDDR5X, 최대 1.2TB/s

- PCIe Gen 6 지원

AI에서 CPU가 왜 중요한가? 전체 추론 파이프라인에서 CPU가 담당하는 작업이 있기 때문이다: 토큰화/역토큰화, KV 캐시 관리, 요청 스케줄링 및 배칭, 전처리/후처리. CPU가 느리면 아무리 GPU가 빨라도 병목이 된다. Vera CPU는 R200 GPU에 끊임없이 작업을 공급하도록 설계됐다.

NVL72 랙 — 실제 배치 단위

개별 GPU보다 중요한 건 랙 단위 성능이다. 실제로 데이터센터에 들어가는 건 NVL72 랙이니까.

| 항목 | Vera Rubin NVL72 | Blackwell NVL72 |

|---|---|---|

| GPU 수 | 72개 (36 슈퍼칩) | 72개 |

| FP4 추론 | 3.6 ExaFLOPS | ~0.9 ExaFLOPS |

| HBM 총량 | 20.7TB | 13.8TB |

| NVLink 대역폭 | 260TB/s (NVLink 6) | ~100TB/s |

| 랙 전력 | ~190kW (MaxQ) | ~120kW |

| 냉각 | 100% 수랭 (최초) | 하이브리드 |

| 조립 시간 | Blackwell 대비 18배 빠름 | — |

3.6 ExaFLOPS. 랙 하나에서 엑사급 연산. 비교를 위해 말하자면, 세계 최고 성능 슈퍼컴퓨터인 Oak Ridge의 Frontier가 GPU 9,408개를 사용해 약 1.2 ExaFLOPS를 달성한다. Vera Rubin NVL72 랙 하나가 AI 추론에서 그 3배 성능을 낸다.

그리고 처음으로 완전 수랭 시스템이다.

NVLink 6: 네트워크가 곧 컴퓨터다

NVLink은 Nvidia의 독점 칩 간 인터커넥트(상호 연결) 기술이다. 랙 내 GPU들이 PCIe보다 훨씬 높은 대역폭으로 통신할 수 있게 한다.

| NVLink 버전 | GPU당 대역폭 | 랙 총 대역폭 |

|---|---|---|

| NVLink 4 (Hopper) | 900GB/s | — |

| NVLink 5 (Blackwell) | 1.8TB/s | ~100TB/s |

| NVLink 6 (Vera Rubin) | 3.6TB/s | 260TB/s |

대규모 모델 학습에서 이것이 중요한 이유: 1조 파라미터 모델은 GPU 한 장에 올라가지 않는다. 여러 GPU에 분산해야 하고, GPU들이 끊임없이 데이터(그래디언트, 활성화 값, KV 캐시)를 교환해야 한다. NVLink 대역폭이 높을수록 통신 대기 시간이 줄고, 실제 연산에 더 많은 시간을 쓸 수 있다.

수랭 냉각: 패러다임의 전환

Vera Rubin NVL72는 Nvidia 최초의 100% 수랭(liquid-cooled) 랙이다. 이것이 중요한 이유:

- 전력 효율: 수랭은 같은 열부하(thermal load)에서 공랭 대비 에너지를 30~40% 적게 사용

- 집적도: 대형 팬과 공기 통로가 필요 없으니 GPU를 더 촘촘하게 배치 가능

- 소음: 극적으로 조용한 운영

- 신뢰성: 움직이는 부품(팬)이 줄어 고장 지점이 감소

이는 미래의 데이터센터가 현재의 공랭 시설과 근본적으로 달라질 것임을 시사한다. 데이터센터를 설계하는 기업들은 처음부터 수랭 인프라를 계획에 포함해야 한다.

Groq 3 LPU — 가장 큰 서프라이즈

Nvidia가 2025년 12월 $20B(약 27조 원)에 인수한 Groq의 첫 Nvidia 협업 제품이다. Groq은 전 Google TPU 아키텍트 Jonathan Ross가 2016년 설립한 회사로, 기존에 자체 LPU 칩으로 Llama와 Mixtral 모델의 초고속 추론을 시연해 주목받았다. Groq의 LPU(Language Processing Unit, 언어 처리 장치)는 GPU와 근본적으로 다른 추론 전용 칩이다. GPU가 범용 병렬 프로세서라면, LPU는 결정론적 추론 가속기(deterministic inference accelerator) -- 실행 경로가 컴파일 시점에 완전히 결정되어, 런타임 스케줄링 오버헤드가 없다.

- 1.2 PetaFLOPS FP8 (LPU 1개)

- 500MB 온칩 SRAM — HBM이 아니라 SRAM이다

- SRAM 대역폭: 150TB/s (Rubin GPU의 HBM4가 22TB/s인 것과 비교)

- 결정론적 지연시간(deterministic latency) — 가변적 실행 경로가 없음

왜 HBM이 아니라 SRAM인가?

SRAM(Static RAM, 정적 랜덤 액세스 메모리)은 트랜지스터 6개로 1비트를 저장하는 반면 DRAM(HBM의 기반 기술)은 트랜지스터 1개와 캐패시터 1개로 1비트를 저장한다. 그래서 SRAM이 DRAM보다 5~10배 빠르지만, 면적(즉 비용)도 그만큼 크다. LPU 하나의 SRAM 용량은 500MB에 불과하다 -- R200의 HBM4 288GB와 비교하면 576분의 1이다.

비결은 LPU가 전체 모델 가중치를 보유하려 하지 않는다는 점이다. 대신 가중치가 칩을 결정론적 패턴으로 흐르는 스트리밍 아키텍처(streaming architecture)로 작동한다. 데이터가 컨베이어 벨트처럼 일정한 속도로 칩을 통과하므로, 캐시 미스(cache miss)나 메모리 지연 같은 GPU의 고질적 비효율이 원천적으로 발생하지 않는다. 결과적으로 추론에서 극한의 처리량을 달성하지만, 모델을 많은 LPU에 걸쳐 분할(파티셔닝)해야 한다.

LPX 랙 구성

Groq 3 LPX 랙(256개 LPU)을 Vera Rubin NVL72 옆에 붙이면, 메가와트당 스루풋이 35배 올라간다. 소형 모델에서는 밀리초 이하의 토큰 지연시간을 달성한다. 대량 추론 서빙과 실시간 애플리케이션에 특화된 구조다.

출하: 2026년 3분기.

자율주행 — "ChatGPT 모멘트가 왔다"

Huang은 자율주행을 키노트의 핵심 주제로 잡았다. 새로운 DRIVE Hyperion Level 4 파트너:

- BYD — 세계 최대 EV 제조사

- 현대·기아 — 전략적 파트너십 확대

- Geely (볼보 모회사), Nissan, Isuzu

그리고 Uber 로보택시:

- 2028년까지 4개 대륙 28개 도시에 배치

- 첫 출발: 2027년 상반기 LA, 샌프란시스코

Uber의 규모가 이 파트너십을 특별하게 만든다. Uber는 전 세계에서 하루 3,000만 건 이상의 운행을 처리한다. 이 중 일부만 자율주행으로 전환돼도 Nvidia 자율주행 플랫폼의 실전 검증 데이터가 압도적으로 쌓인다.

개발자가 알아야 할 것

CUDA 20주년 + 에이전트 툴킷

- CUDA Toolkit 13.1.1 (2026년 1월 릴리스) -- 전 세계 500만 명 이상의 CUDA 개발자가 사용하는 플랫폼

- cuBLAS 독립 패치: 이제 CUDA 전체 업데이트 없이 cuBLAS(기본 선형대수 서브루틴 라이브러리)만 업데이트 가능

- NVIDIA Agent Toolkit (오픈소스): 기업용 자율 AI 에이전트 빌드

- NemoClaw: 로컬에서 장기 실행 AI 에이전트를 개발/배포하는 오픈소스 스택. 에이전트 오케스트레이션(orchestration, 여러 에이전트 간 작업 조율) 프레임워크, 다단계 추론을 위한 메모리 관리, 도구 사용(tool-use) 통합, 클라우드 의존 없는 로컬 배포를 지원한다

Agent Toolkit을 쓰는 기업 목록: Adobe, Atlassian, Salesforce, SAP, Siemens, ServiceNow, Red Hat 등.

DLSS 5 — 업스케일링이 아니다

DLSS 5는 기존의 업스케일링(저해상도 이미지를 고해상도로 변환)이나 프레임 생성을 넘어서, **"Real-Time Neural Rendering(실시간 신경망 렌더링)"**이라는 새로운 접근이다. 기존 래스터라이제이션(rasterization, 3D 장면을 2D 픽셀로 변환하는 전통적 방식) 파이프라인의 일부를 신경망이 대체해, 조명 반사와 재질 상호작용까지 포함한 완전한 픽셀을 직접 생성한다. RTX 50 시리즈용, 2026년 가을 출시.

로드맵 — 2028년까지

| 세대 | 시기 | 핵심 |

|---|---|---|

| Rubin | 2026 H2 | 3nm, HBM4, 50 PFLOPS |

| Rubin Ultra | 2027 | 컴퓨트 칩렛 4개, ~100 PFLOPS, 1TB HBM4E |

| Feynman | 2028 | TSMC 1.6nm(A16), 3D 다이 스태킹, NVL1152 스케일 |

Feynman이 특히 주목할 만하다. Nvidia 최초의 3D 다이 스태킹(die stacking, 칩을 수직으로 적층하여 면적 효율과 대역폭을 높이는 기술) GPU이고, TSMC의 차세대 1.6nm(A16) 공정을 사용한다. 그리고 NVL1152 -- 한 클러스터에 GPU 1,152개로, 현재 NVL72의 16배 규모다.

핵심 인용

"Every SaaS company will become an Agent-as-a-Service company." — Jensen Huang, GTC 2026

"The ChatGPT moment for autonomous driving is here." — Jensen Huang, GTC 2026

"GeForce is Nvidia's greatest marketing campaign." — Jensen Huang, CUDA 20주년 기념

개발자에게 주는 의미

- 추론 비용이 계속 하락할 것이다: 더 효율적인 하드웨어는 토큰당 비용 하락을 의미한다. 서비스 가격 모델을 이에 맞게 설계해야 한다.

- 수랭 냉각이 이제 필수: 데이터센터 공간을 설계하거나 임대한다면, 수랭 인프라를 1일차부터 반영해야 한다.

- 에이전트 프레임워크가 주류로 진입: Nvidia의 NemoClaw와 Agent Toolkit 투자는 자율형 AI 에이전트가 다음 플랫폼 전환(platform shift)임을 시사한다.

- GPU 해자(moat)는 그 어느 때보다 넓다: 경쟁에도 불구하고, CUDA + NVLink + 생태계 조합은 복제가 극도로 어려운 우위다.

경쟁 구도와 배경 지식

커스텀 실리콘 — 빅테크의 자체 칩

Google(TPU v6), Amazon(Trainium3), Microsoft(Maia 2)가 자체 AI 칩 개발을 지속하고 있다. 이들은 주로 내부 사용과 자사 클라우드 플랫폼용으로, Nvidia 의존도를 줄이려는 전략이다. 다만 이들 칩이 일반 시장에 판매되지 않으므로, Nvidia의 독립 개발자 및 기업 시장 지배력은 유지된다.

AMD MI400 vs Nvidia Rubin

AMD는 2026년 하반기 MI400(코드명 "Antares") 출시를 예고했다. CDNA 5 아키텍처, TSMC 3nm, HBM4 지원, 그리고 ROCm 7.0 소프트웨어 스택이 함께 나온다. Nvidia가 독점하던 AI 학습 시장에서 AMD가 점유율을 10%대까지 끌어올린 상태다. 특히 추론(inference) 워크로드에서 AMD의 가격 대비 성능이 주목받고 있다. 하지만 Nvidia의 진짜 해자(moat, 경쟁 우위)는 하드웨어가 아니라 CUDA 생태계다. PyTorch, TensorFlow, vLLM 등 주요 AI 프레임워크가 모두 CUDA에 최적화되어 있고, 20년간 쌓은 500만 명의 개발자 커뮤니티를 단번에 따라잡기는 어렵다.

Intel Falcon Shores — 조용한 3위

Intel의 AI 가속기 Falcon Shores는 2026년 출하 예정이지만, 시장 반응은 미지근하다. 전작 Gaudi 3가 Nvidia H100 대비 추론 가격 대비 성능에서는 경쟁력을 보였으나, 소프트웨어 생태계와 호환성 문제로 기대만큼 채택되지 못했다. Intel은 AI 칩 사업을 별도 법인으로 분사할 가능성까지 언급되고 있다.

국가별 AI 인프라 경쟁

GTC에서 Huang이 강조한 또 다른 키워드는 "Sovereign AI(주권 AI)" -- 각국이 자국의 데이터와 AI 역량을 자국 내 인프라로 확보하려는 움직임이다. 사우디, UAE, 프랑스, 일본이 자국 내 AI 데이터센터를 대규모로 건설 중이며, 이는 데이터 주권(data sovereignty)과 안보 우려가 주된 동기다. 이 흐름이 Nvidia의 주문 파이프라인 $1T의 핵심 동력이다. 한국도 2026년 국가 AI 컴퓨팅 인프라 확충 계획을 발표했으며, KT와 SK텔레콤이 Nvidia DGX 클라우드를 도입 중이다.

GPU 컴퓨팅의 역사적 맥락

2012년 AlexNet이 ImageNet 대회에서 GPU를 사용해 우승한 이후, GPU는 AI의 핵심 하드웨어가 됐다. Nvidia의 시가총액은 2012년 $10B에서 2026년 $4T로 400배 성장. 이 성장의 95% 이상이 AI 수요 덕분이다.

참고 자료

관련 기사

NVIDIA GTC 2026: 에이전틱 AI가 주인공, Vera CPU로 병목 깨겠다

GTC 2026의 핵심은 에이전틱 AI야. AI가 챗봇에서 자율 에이전트로 진화하면서 CPU가 새로운 병목이 됐어

OpenAI, Cerebras에 $20B 쏟으며 지분까지 — Nvidia 의존 빼는 중

OpenAI가 Cerebras에 3년간 $20B+를 지불하고 웨이페어(warrant)로 최대 10% 지분을 취득할 수 있는 딜이 공개됐어. 추론 비용·전력 병목·Nvidia 의존도를 한 번에 건드리는 수.

Micron 매출 3배 폭증 — AI가 메모리 반도체 지형을 통째로 바꾸고 있어

Micron 2분기 매출 $23.86B, 전년 대비 3배. HBM 수요 폭발, 다음 분기 $33.5B 전망, 설비투자 $25B. AI 메모리 슈퍼사이클의 모든 것.

AI 트렌드를 앞서가세요

매일 아침, 엄선된 AI 뉴스를 받아보세요. 스팸 없음. 언제든 구독 취소.